提高功率密度和優化成本一直都是高效大功率應用的主要發展方向,尤其是在電動汽車等細分市場。為此,英飛凌宣布其應用于高壓MOSFET的理想封裝技術——QDPAK和DDPAK頂部散熱(TSC)封裝技術已成功注冊成為JEDEC標準,以便盡快與行業上下游各環節的企業分享這一成果。同時,英飛凌于近日召開媒體會,由英飛凌科技電源與傳感系統事業部大中華區應用市場總監程文濤,對該技術的工作機理、技術優勢等做出深入解讀。

英飛凌科技電源與傳感系統事業部大中華區應用市場總監 程文濤

英飛凌科技電源與傳感系統事業部大中華區應用市場總監 程文濤

程文濤全面闡述了英飛凌QDPAK、DDPAK頂部散熱封裝技術,從開發頂部散熱封裝技術的初衷,技術創新發展的過程,到適宜的應用和落地實踐,再到如今成功入選JEDEC標準的原因以及對整個半導體行業的重要意義等,涵蓋了方方面面。

頂部散熱(TSC)封裝 QDPAK和 DDPAK的前身,其實是大家熟悉的DPAK(TO252)封裝。QDPAK大致相當于4個DPAK并排,DDPAK則是兩個DPAK并排(Double DPAK),這類封裝的主要優勢在于:

滿足更大功率需求:優化利用電路板空間,采用開爾文源極連接,減少源極寄生電感;

提高功率密度:頂部散熱可實現最高電路板利用率;

提高效率: 經優化的結構具有低電阻和超低寄生電感,可實現更高效率;

減輕重量:綜合優化散熱和發熱,有助于打造更小巧的外殼,從而減少用料,減輕重量

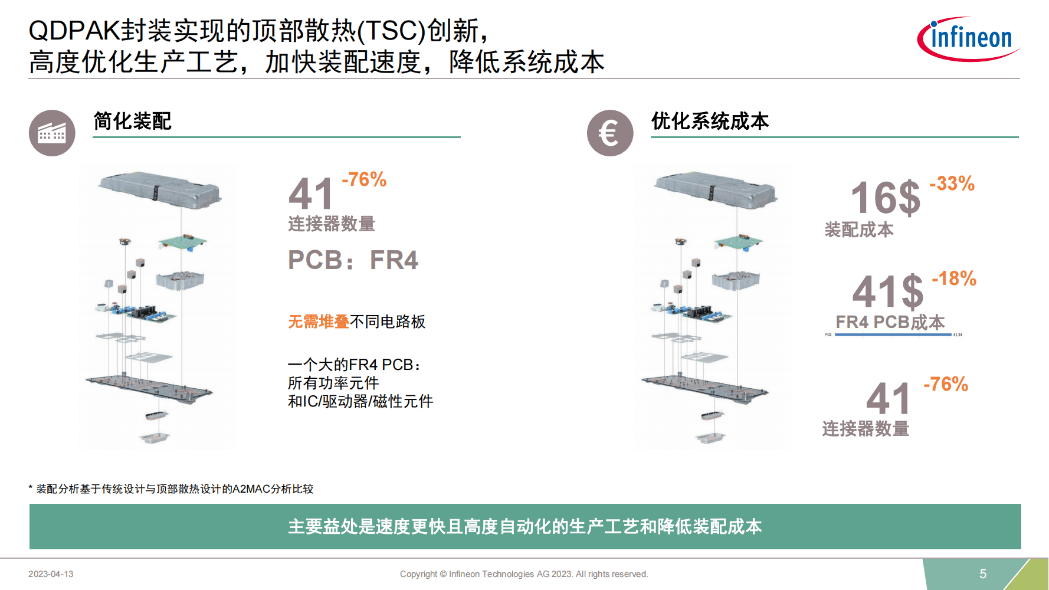

程文濤表示,這兩種頂部層散熱封裝技術在用戶層面能夠解決的問題包括,讓整個裝配過程步驟變少,自動化制造流程更簡潔,最終在下游廠商端實現包括PCB數量、層級和板間連接器用量減少,帶來裝配及整體系統成本大幅降低。

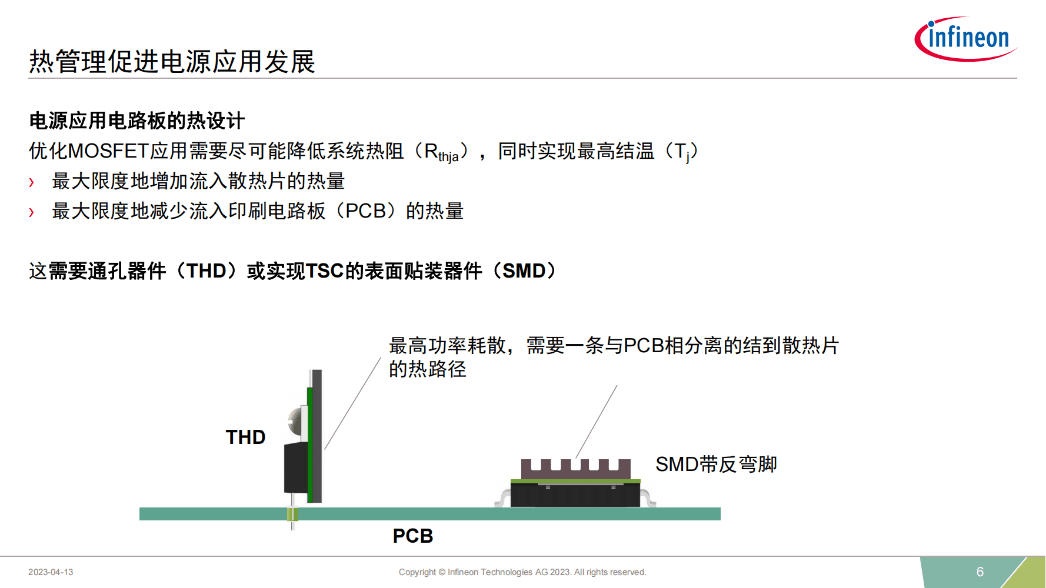

優化MOSFET應用需要盡可能降低系統熱阻(Rthja),同時實現最高結溫(Tj)。如此一來能夠最大限度地增加流入散熱片的熱量,并最大限度地減少流入PCB的熱量。

熟悉功率半導體行業的讀者應該還有印象,10年前的大功率應用器件(千瓦及以上的功率)基本以通孔器件封裝(THD)為主,例如大家熟知的TO247、TO220封裝。這類插件封裝的優勢在于,在當時的裝配和封裝工藝下能最大限度地利用外加散熱片,高效地把芯片內部產生的熱量帶出芯片,讓芯片能夠工作在大功率應用場景中。

但隨著數據中心、4G及5G無線通信宏基站等設備對于功率密度的要求越來越高,設備尺寸越做越小,開始要求電源應用的電路板設計中采用更少或不用獨立散熱片,同時把更多的熱量均勻地散發到整個設備之外。

貼片化是從帶獨立散熱片的插件封裝,走向更高功率散熱的第一步。但這對于緊貼PCB表面的貼裝器件(SMD)來說,很難做到。

“這是兩個很矛盾的需求,尤其在最近的5年之內越來越凸顯。我們用了很長時間與產業鏈下游的行業頭部客戶以及工程師討論,最終達成共識,就是頂層散熱才是解決這個矛盾的根本途徑。” 程文濤說到。

如上圖(左)所示,一般貼片封裝器件的散熱主要靠芯片底部與PCB之間的接觸,靠PCB銅箔把芯片產生的熱量傳導出去。這樣做的壞處是需要耗費較大的PCB銅箔面積,才能有效散熱,如果銅箔不夠大,在芯片底部就會形成一個熱點,給PCB帶來很大壓力。

目前業界常用的PCB材質均為FR4,這類材質在業界標準中存在110度左右的最高溫度上限。在這樣的要求下,如果利用貼片和PCB之間的結合均勻地將更多熱量傳遞出去是個挑戰,在這方面,底部散熱封裝慢慢地走到了瓶頸。

而上圖(右)顯示在使用增加散熱片的頂部散熱模式后,可以不靠底部銅箔散熱,在同樣的PCB材質下,能夠更有效、更均勻地把熱量散出去。如此一來給用戶帶來的好處是,在同樣的散熱面積下,設備整體能夠傳遞出的功率耗散得到了增加。

注冊成為JEDEC標準三大動因:

至于將QDPAK和DDPAK頂部冷卻(TSC)封裝技術注冊成為JEDEC標準,主要也是基于JEDEC這個標準組織有能力將行業里的一些創新想法快速推行開。JEDEC標準本身是免費的,技術在JEDEC標準組織中得到了注冊和認證之后,其它的廠商可以免費從JEDEC標準組織里面下載及查看,廠家要做的就是制造符合這個標準的產品。因為已經跟業界通行的尺寸、安規都是相兼容的,所以為產品做推廣的時候就更加方便。再者,JEDEC標準在半導體行業中認可度比較高。最后一點,在功率半導體領域業界有一個不成文的規定,任何一家廠商在選定一款功率半導體時,至少需要一個備選方案,理想的情況是有多種備選方案,也就是Multiple Source,所以標準本身就顯得至關重要。

標簽: 行業新聞 點擊: 評論: